# Using Software Technology To Specify Abstract Interfaces In VLSI Design

TR85-017 1985

Richard Rutter Gross

The University of North Carolina at Chapel Hill Department of Computer Science CB#3175, Sitterson Hall Chapel Hill, NC 27599-3175

$UNC\ is\ an\ Equal\ Opportunity/Affirmative\ Action\ Institution.$

# USING SOFTWARE TECHNOLOGY TO SPECIFY ABSTRACT INTERFACES IN VLSI DESIGN

Richard Rutter Gross

The views expressed in this dissertation are those of the author and do not reflect the official policy or position of the Department of Defense of the U.S. Government.

# USING SOFTWARE TECHNOLOGY TO SPECIFY ABSTRACT INTERFACES IN VLSI DESIGN

bу

# Richard Rutter Gross

A dissertation submitted to the faculty of the University of North Carolina at Chapel Hill in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science.

Chapel Hill

1985

Approved by:

Advišot

W.

Reader

RICHARD RUTTER GROSS. Using Software Technology to Specify Abstract Interfaces in VLSI Design. (Under the direction of PETER CALINGAERT.)

#### **ABSTRACT**

Good techniques for VLSI design change management do not now exist. A principal reason is the absence of effective methods for the specification of abstract interfaces for VLSI designs. This dissertation presents a new approach to such specification, an approach that extends to the VLSI domain D.L. Parnas's techniques for precise specification of abstract software design interfaces to the VLSI domain. The proposed approach provides important new features, including scalability to VLSI design levels, integration into the design life-cycle, and a uniform treatment of functional, electrical, and geometric design information. A technique is also introduced for attaching a value to the degree of specification adherence of a candidate module.

To illustrate and evaluate the proposed approach, an example specification method using it is described and evaluated experimentally.

# ACKNOWLEDGMENT

J.S. Bach acknowledged his work with the Latin phrase Soli Deo Gloria ("Glory to God alone"). If he, being great, made such an acknowledgment, how can I or anyone else do other?

One especially noteworthy area of God's help to me has been His provision of a supremely patient and encouraging wife and family. Without them, I could certainly never have finished this work.

I am also grateful to have been able to participate, while this dissertation work was being conducted, in a collateral research project funded by Semiconductor Research Corporation Grant No. 41258. This dissertation has greatly benefited from the discussions I had with the other participants in that project.

# CONTENTS

| 1. Introduction                                                              | 1             |

|------------------------------------------------------------------------------|---------------|

| 1.1 Definition of the Problem                                                | 1             |

| 1.2 Potential Contribution from Software Engineering Techniques              | $\frac{1}{2}$ |

| 1.3 Determination of Research Objectives                                     | 3             |

| 2. Survey of Previous Research                                               | 11            |

| 2.1 Definitions                                                              | 11            |

| 2.2 Requirements for VLSI Design Abstract Interface Specifications           | 19            |

| 2.3 Existing VLSI Design Interface Specification Methods                     | 23            |

| 2.4 Parnas's Techniques for Abstract Interface Specification                 | 35            |

| 2.5 Summary                                                                  | 38            |

| 3. An Abstract Interface Specification Approach for VLSI Designs             | 39            |

| 3.1 Overview and Description of the Approach                                 | 39            |

| 3.2 Example                                                                  | 53            |

| 3.3 Composition of Specifications                                            | 63            |

| 3.4 Simplifications to the Approach Permitted by VLSI Design Characteristics | 73            |

| 4. Technique Effectiveness                                                   | 77            |

| 4.1 Experimental Design                                                      | 77            |

| 4.2 Experimental Results                                                     | 81            |

| 5. Conclusion                                                                | 95            |

| 5.1 Principal Conclusions                                                    | 95            |

| 5.2 Suggestions for Future Work                                              | 97            |

| Appendices:                                                                  |               |

| A. Specifications of Modules in Test Set                                     | 101           |

| B. Illustration of Specification Execution                                   | 131           |

| Bibliography                                                                 | 145           |

#### CHAPTER 1

#### INTRODUCTION

# 1.1 Definition of the Problem.

VLSI design is integrated circuit design in which brute force no longer works. The major concern in VLSI design is the management of complexity [Mudg81, Séqu83], not just putting together a system with whatever means are handy.

Traditional techniques for complexity management, such as hierarchy, restriction, and structuring, have been applied in the VLSI context: nevertheless, the design process is still costly, and hundreds of designer-years are being invested in the development of state-of-the-art VLSI circuits [Latt81, Cane83]. The unconstrained nature of the VLSI design medium leads to some of this cost [Séqu83], in that only inefficient algorithms are available to apply to the typically NP-hard problems, such as one-dimensional placement [Valt82] and optimal routing [John82], encountered in design construction and verification. Nevertheless, while such traditional costs of VLSI design are still the subject of much research, another source of cost, only lately recognized, is becoming a major concern among designers. This cost arises from the ripple effect of changes during the design process [Wern83], and its seriousness stems from its particular sensitivity to the increases in complexity that characterize modern VLSI design. Belady and Lehman's work [Bela79], for example, suggests that for software systems "increasing system complexity leads to a regenerative, highly non-linear, increase in the effort and cost of system maintenance and also limits ultimate system growth." While similar studies, to my knowledge, have not yet been directed specifically at VLSI systems evolution, there is good reason to suspect that the effects of progressive changes on VLSI systems are comparable.

Furthermore, this "cost of change" compounds in the following way. Competitive pressures for denser, more capable, and hence more complex circuits beget increased refinement of designs, or increased change. Such increased change, Werner notes, is necessitated by elevated performance standards for modern chips, possibly even requiring retrofitting a design in progress to include new technologies or capabilities. However, the same competitive pressures also demand early production of these more-complex chips, so that larger teams, partitioning the design task, are assembled to meet delivery schedules accelerated by intense competition. Increasing complexity thus has two effects: (1) more change; and (2) larger design teams. As Brooks [Broo75] notes,

either effect alone increases the amount of communication required in the design project, and the cost of this communication must be added to the amount of design work to be done. The combination of these effects compounds costs of communication and thus of design, making the cost factors of design in the multi-designer environment significantly different from those that have been traditionally applied.

Consequently, as VLSI circuits grow larger, the cost of change management, especially in the now-typical multi-person design effort, may well become the primary concern in the VLSI design process. Because current VLSI design techniques focus primarily on developing correct initial designs and not yet on the management of design change, the development and study of VLSI design change management techniques are timely and important.

## 1.2 Potential Contribution from Software Engineering Techniques.

There have been numerous recent suggestions (for example, see [Rade82, Kuni84, Musa85]) that transfer of design technology from software engineering, which has dealt with systems with similar numbers of components for at least a decade, might either improve the theoretical base for VLSI design or at least enhance the effectiveness of emerging VLSI design methodologies. Séquin [Séqu83] supports this suggestion by listing the following software design characteristics that possess counterparts in VLSI design.

- a. Appropriate design representations are crucial to design success.

- b. Abstraction provides an appropriate vehicle for dealing with complexity. The possibility of exploiting such abstractions, using high-level languages, is promising.

- c. At the lowest level, on the other hand, the design may be restricted to a limited set of wellunderstood constructs.

- d. The design task can be partitioned and structured. For example, functional design can be separated from implementation.

- e. Testing of the final realization against a well-defined system specification is essential.

- f. "Of crucial importance in the construction of large and complex systems is a good set of tools and a suitable design method."

In contrast to VLSI design, software engineering has seen much research directed toward design methodologies, and the application of principles from these methodologies to VLSI design is a promising and relatively unexplored idea. Such adaptation of software engineering methodologies

to VLSI design is certainly nontrivial, because the latter must take into account additional concerns such as geometric and electrical limitations. Nevertheless, it is readily conceivable that transfer of concepts from software engineering could contribute to the development of an improved theoretical base in VLSI design. Such improvement would aid both the teaching of VLSI design principles and the construction of more capable automated design tools.

Despite the quantity of methodological research in software engineering, however, most modern software design methodologies do not specifically address the factor of change in the design process. In this regard, the software design techniques of D.L. Parnas are conspicuously exceptional. His techniques, specifically those of information hiding, hierarchical structuring for design families, and precise specification, have demonstrated the potential to become the nucleus of a coherent approach to the software change management problem. The overall motivation for my current research, then, has been to investigate how these techniques can be applied to manage change in the VLSI design process.

# 1.3 Determination of Research Objectives.

A research program that conscientiously investigates the transferability of Parnas's techniques to VLSI design change management would include:

- a. An extension of information hiding, hierarchical structuring for families of designs, and precise specification into the VLSI domain by:

- (1) developing a realistic model of the contemporary VLSI design process;

- (2) identifying in the model the points at which decisions crucial to the techniques are made;

- (3) constructing for these decision points a set of criteria that guide effective design change management.

- b. The development of an integrated set of VLSI tools that enable a designer to use the criteria developed in task a to manage design change.

c. An assessment of the effectiveness and extensibility of the design change management procedure so devised.

The scope of such a research program clearly exceeds that of a single dissertation. Consequently, it has been necessary to identify and order the component research problems embodied by this program.

1.3.1 Component Research Problems and Their Interdependencies.

1.3.1.1 Specifying Abstract Interfaces for VLSI Designs.

Britton, Parker, and Parnas [Brit81a] define an "interface" between two programs as "the set of assumptions that each programmer needs to make about the other program in order to demonstrate the correctness of his own program." An abstract interface specification, in their sense of the term, has been carefully limited in content to a description of only these assumptions, so that the specification describes not a single interface but a class of interfaces. More than one module or design thus fits the interface, and the interface is robust under certain types of changes.

Abstract interface specification of VLSI design modules is a largely unstudied problem. This lack of attention is surprising in light of the growing realization that existing VLSI design specification techniques are inadequate:

there are no real tools for developing and simulating high-level specifications, so most work must be done by hand. There are also problems with casting the specification in the proper form....The process of specification is intimately involved with the kinds of design tools available [Wall84].

I believe that the primary reason for this inadequacy is that most references to "specification" in VLSI are to clear-box specifications, frequently at the logic level. Clear-box specifications address module interfaces only indirectly, by prescribing an implementation of internal module logic or circuitry. Clear-box specifications, then, blur architectural and implementational concerns; abstract interface, or "black-box," specifications keep these concerns separate. At VLSI complexity levels, separation of these concerns is essential. Clear-box specification techniques do not scale up, as can be plainly seen from the difficulty of inferring the function from even an MSI-level circuit diagram. More seriously, however, the merging of architectural and implementation issues in large-scale system design significantly hinders the partitioning of the design task and degrades (if not destroys) the conceptual unity, hence the usefulness and robustness to change, of the resulting system [Blaa81]. The development of effective abstract interface specification techniques for VLSI designs is thus of critical importance.

## 1.3.1.2 Quantifying Ease of Change of VLSI Designs.

One criticism justly raised about methodological research is that claimed benefits for proposed methods are frequently unsubstantiated. To avoid this criticism, one would like to have an impartial means of quantifying the degree to which a given VLSI design is easy or difficult to change; then, based on this quantification, the merits of various change management techniques could be compared.

Preliminary investigation into quantifying ease of change suggests that, first, a metric is needed for change itself, so that the "difference" between two VLSI designs can be measured. A modest amount of experimentation into developing a change metric was conducted in the context of this exploration [Gros84]. This experimentation investigated measuring VLSI design change as a difference in design information content, going on to attempt to measure design information by counting various discrete design components (analogous to software science approaches such as those described by Halstead [Hals77], McCabe [McCa76], or Albrecht and Gaffney [Albr83]). Techniques employing such approaches will probably need to be complex to capture design information content successfully. Further, there may be assumptions embedded in the design that render desirable information components uncountable, suggesting that such metrics must be derived from a design representation that also embodies these assumptions. An abstract interface specification for the design is such a representation.

#### 1.3.1.3 Using Information Hiding in VLSI Design Modularization.

The decomposition of a VLSI design into modules is an important phase of the design process. In a study of decomposition criteria, Heath [Heat83] has found that information hiding [Parn72b, Brit81a] is a desirable basis for VLSI design decomposition whenever robustness under change is a primary design objective. At the same time, however, he notes that VLSI design modularization, using any criterion, requires the external aspects of each module to be "sufficiently and precisely specified." Because information hiding and modularization are so directly interconnected, precise interface specification techniques for VLSI designs are essential if the benefits of information hiding are to be obtained.

#### 1.3.1.4 Creating Broad Families of VLSI Designs.

Parnas [Parn76a] characterizes a set of programs as a family "whenever it is worthwhile to study programs from the set by first studying the common properties of the set and then determining the special properties of the individual family members." It would be useful to learn whether considering the successive versions of an evolving VLSI design as a family has the potential to reduce the cost of VLSI design development and maintenance. There is some evidence in the affirmative [Gros83b].

Nevertheless, exploiting the family concept depends critically on the availability of precisely-specified intermediate designs that can serve as checkpoints for design backtracking. To the extent that these intermediate designs can be characterized by their interfaces, progress in research seems to hinge once again on the availability of techniques for VLSI design interface specification.

1.3.1.5 Determining Extent of Required Revalidation Following VLSI Design Change.

The decision to change a VLSI design brings about the following activities.

- a. Determine the nature and scope of the change required.

- b. Perform the change.

- c. Ensure the correctness of the design by testing following the change.

Full testing of the design following each change, however, is costly and often unnecessary. Unfortunately, there currently exist no suitable ways to determine which subsets of the design might have been affected by a given change; thus one cannot be sure that anything less than full testing will suffice. Techniques are required to assist the designer in making such a determination.

This problem is a chief reason that information hiding was developed in the software domain. An extension of information hiding to VLSI design that would address this problem requires that an abstract interface be specified at the boundaries of each design component to which change effects are to be localized. The existence of such a specification would reduce testing of any changed design to the assurance that each changed module continued to meet its interface specifications. Even if such interface specifications were not met, the affected boundary modules would be clearly identified for follow-on modification and testing.

#### 1.3.2 Dissertation Overview.

The dissertation is organized as follows. Chapter 2, after defining key terms and criteria, summarizes the research reported in the literature to date in developing methods for VLSI design interface specification. In chapter 3, I present an abstract interface specification method, an extension of Parnas's software specification techniques. I do not contend that either the specific method described, or the notation used to express it, is optimal; rather, I argue for the desirability of the approach thus exemplified.

Its advantages and disadvantages are as follows:

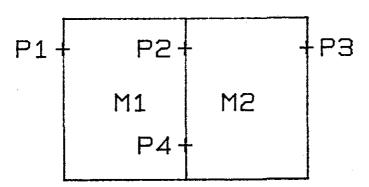

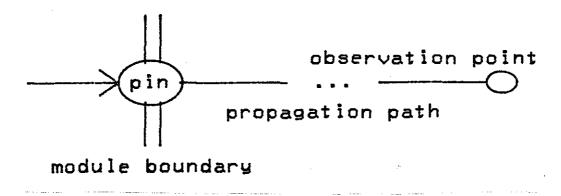

- The approach achieves practical scalability to VLSI design levels through precise partitioning of concerns and the exploiting of abstraction: the complexity of the specification appears to grow slowly with design scale. Pressing the separation of concerns to the ultimate, I made a major decision, to partition module semantics per-pin (instead of per-module, as is conventional). This radical partitioning enhances scalability, complexity control, and change management, at the cost of making it somewhat more difficult to specify constraints global to the module.

- The proposed specification starts by capturing high-level concerns that are then evolved into more particular specifications as details become available over the course of the design. The specification not only evolves in detail, it remains an active component of the design, subject to intentional revision occasioned by new insights from the detailing.

- The same mechanisms are used for each of functional, electrical, and geometric information.

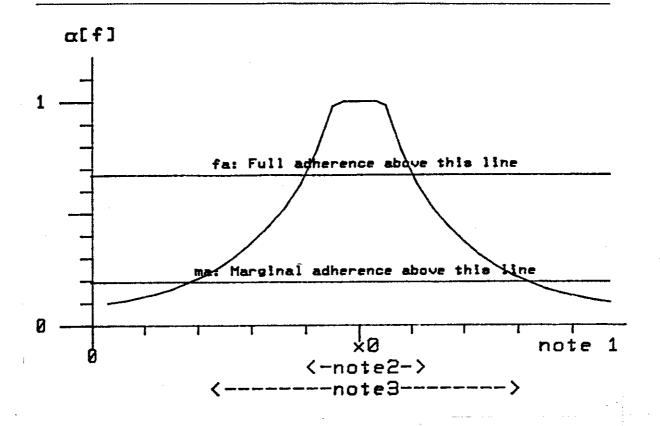

- A new technique is included for attaching a value to the degree of specification adherence of a candidate module. Using this technique, the specifier can communicate knowledge of the marginal utility of design tradeoffs to the implementer. The technique is complex, however, and needs to be made more efficient to be practical.

The proposed interface specification method consists of:

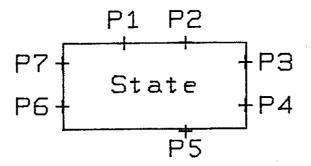

— A black-box finite-state-machine model, together with a generic data type for pin and internal state variables (the generic state type) identifying the level of the specification. Specification refinement corresponds to evolutionary refinement of this data type. Data type syntactic and semantic components are distinguished, the former being statically verifiable and the latter requiring dynamic verification. This partitioning of concerns permits further simplification.

- An extension of Parnas's access function as a key specification element, partitioning module function into per-pin components.

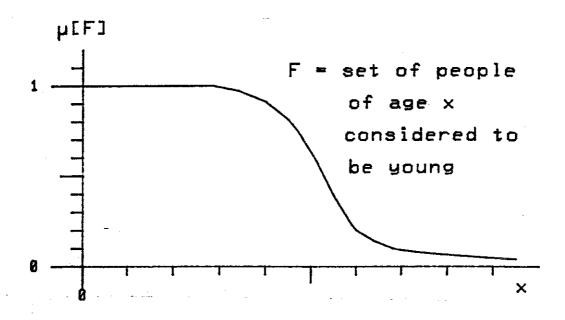

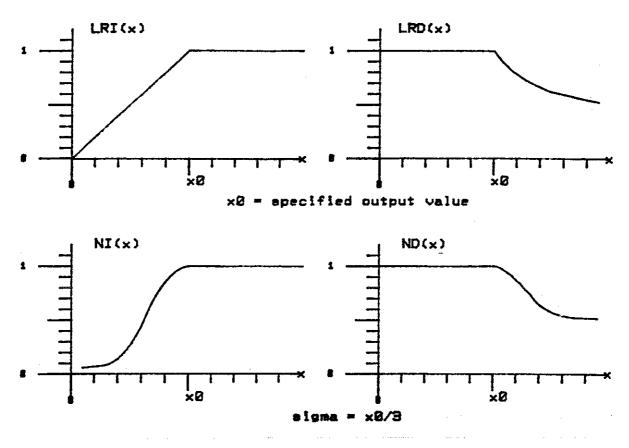

- Adherence functions, which attach a value to the degree to which a module adheres to a given specification. Specification adherence is defined in terms of a Zadeh fuzzy set [Zade75, Zade84].

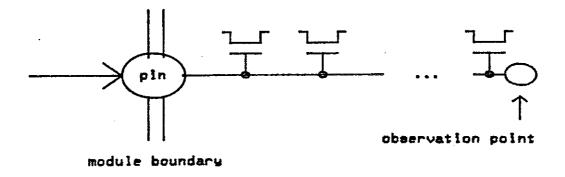

I next discuss sequencing and performance issues in the composition of such specifications. I show how access functions are treated as "communicating sequential processes" (CSP) in Hoare's sense, and show how his CSP notation can be used to express these functions. I also address four issues relating to such use of CSP:

- The power of CSP as an interface specification notation.

- Rules of thumb for expressing data and control pin access functions in CSP.

- The degree of module function partitioning that can be attained in various situations. The worst case is one in which a single master control pin effects all module function.

- Requirements of a base language for implementing CSP. CSP is a notation, not a language.

In closing chapter 3, I cite specific characteristics of the VLSI design process that might be used to simplify specifications. In general, these involve restrictions on the general model:

- Restriction to the use of a standard, portable base language.

- Restriction of the specification refinement hierarchy to certain predefined semantic and syntactic levels, promoting reusability of generic state type definitions.

- Restriction of the adherence function space to a set of standard adherence functions (candidates are presented).

In chapter 4, I report on an evaluation of the proposed abstract interface specification method with respect to the criteria established in chapter 2. The evaluation is based on experience with a set of four real small- to large-scale IC modules which were specified, using the proposed method, at various semantic and syntactic refinement levels. These specifications are provided in an appendix.

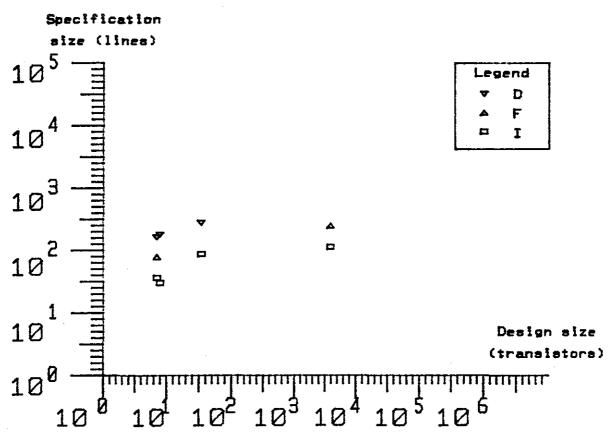

— To evaluate the perceived cost-effectiveness (scalability) of the method at VLSI design levels, I consider specification size as a function of design size. The data suggest that this specification approach is feasible for very-large-scale designs.

- To test the life-cycle integration of the method, I first measure the relative amount of change in the test specifications as they are refined, finding that a significant fraction of each test specification is preserved unchanged through refinement.

- To examine the spareness of the method, I informally review each of its elements for overlap with the others.

- To estimate the method's effectiveness in managing change, I conduct a series of experiments. The first demonstrates the robustness of subordinate specifications when a parent specification is changed. The second illustrates the conditions under which specification changes affect nearby modules. In the third, real-world changes are applied to an actual specification with only minor effects.

Chapter 5 contains conclusions and suggestions for future research.

,

#### CHAPTER 2

#### SURVEY OF PREVIOUS RESEARCH

The previous chapter suggested that effective techniques for specification of abstract VLSI design interfaces would help manage change in the VLSI design process. This chapter will describe and evaluate the effectiveness of existing VLSI design interface specification methods.

Some historical background will place this survey in context. A rough parallel can be drawn between the evolution of design methodologies for software and for integrated circuits, although the paths are offset in time by perhaps 10-15 years. In the software community, there was little recognition of the importance of specifications before system complexity exceeded manageable bounds. Even now (as Yeh [Yeh83] observes), certainly not all software designers have internalized the recognition that the complexity of modern systems is truly beyond their intellectual span of control. One expects, therefore, a parallel reluctance by IC designers to admit that complexity has become overwhelming. Because MSI and LSI complexity levels do not compel an emphasis on specification, "specification" and "interface" are terms that have yet been mentioned only infrequently in the IC design literature.

This is not to say that the specification and interface definition functions have not been performed in IC design, or even in VLSI design. These functions, however, have been called by different names, leading to some semantic confusion. To define them clearly here, I will first provide a model of the VLSI design process, a model that will show the role of VLSI design interface specifications. Based on this model, I will define "VLSI design abstract interface specification." Finally, I will survey the important published work that has been done so far in developing VLSI design interface specification techniques.

# 2.1 Definitions.

# 2.1.1 The Integrated Circuit (IC) Design Process; the VLSI Design Process.

Definitions. The IC design process is a sequence of elaborations that synthesize, from a design concept, a form suitable for fabrication. The VLSI design process is the IC design process applied to the design of very-large-scale circuits.

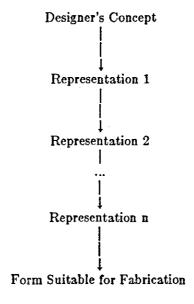

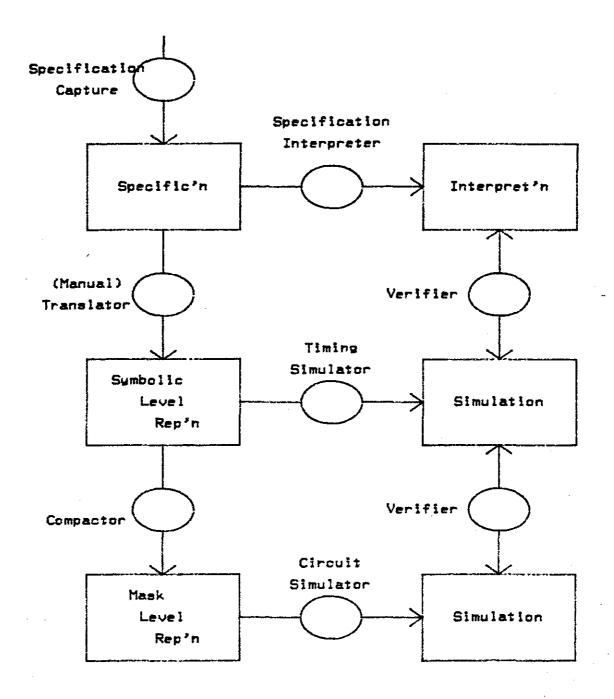

Discussion. Figure 2-1 illustrates a hierarchical model of the contemporary IC design process. The designer starts with a concept, either of the complete system or of a system component. The goal of the design is a description of the design in a form suitable for fabrication [Trim81]. To manage complexity, the designer subdivides the monolithic concept-to-fabrication transformation into a sequence of elaboration steps, the result of elaboration (synthesis) at each each step being an intermediate representation (or "description"; cf. [Lehm84]). Each representation, then, contains more information, in Shannon's sense [Shan49], than its predecessor; it serves as a milestone in the descent of a tree of potential designs that could be developed from the original concept. Representations frequently employed in IC design are, for example, the floorplan, the logic diagram, the layout, and so on; each embodies additional information about the design.

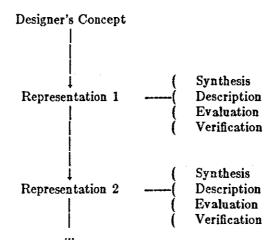

Synthesis and representation, however, are not the only activities that take place at each elaboration step. Two additional activities — verification and evaluation — are required at each step to ensure the accurate progress of the design effort (Figure 2-2). Redoing the current step or backtracking to a previous step may be required.

Figure 2-1. The IC Design Process.

The IC design process, therefore, is the hierarchical repetition, possibly with backtracking, of the four steps defined in Figure 2-2. Furthermore, in the IC system design process, Figure 2-1 should be visualized as being replicated many times, once for each design component (such as a cell), so that a representation of the total design consists of a compatible set of representations for all components.

The definition of the VLSI design process correctly identifies its component activities as the same as those for IC design. As I noted in chapter 1, however, "VLSI design is IC design in which brute force no longer works." The requirement for using complexity management techniques in the design elaborations distinguishes VLSI design from IC design at lesser levels of integration.

# 2.1.2 Interface; Abstract Interface.

Definitions. An interface (between two design modules) is the set of assumptions that each module designer needs to make about the other module to demonstrate the correctness of his/her own module. An abstract interface is an interface containing no assumptions about the internal composition of the module.

Figure 2-2. Activities Performed at an IC Design Step. [Boeh81, Latt81, Dall83]

<sup>-</sup> Synthesis: the elaboration of one level of description into the next lower level.

<sup>—</sup> Description: the construction of an abstract model of a system (a representation) that details properties specific to a given purpose.

<sup>-</sup> Verification: a semi-formal process whereby the design at a particular level is shown to be equivalent, in either behavior or structure [or both], to one or more higher-level designs.

<sup>—</sup> Evaluation: the assessment of the degree to which the design meets (1) physical and performance requirements and constraints; and (2) criteria of behavioral and structural completeness.

I have shortened Lehman, Stenning, and Turski's phrase "frame of reference for establishing correctness" simply to the word *frame*. A physical frame both constrains and allows freedom within its constraints; thus it is an accurate model of a specification.

Supporting this interpretation, Levene and Mullery [Leve82] identify the role of a specification from a traditional administrator's viewpoint, but still define it as a frame:

- [A specification] should clearly indicate what the intended system is to do, including interaction with other systems, people, media, and devices, in terms that the customer or users can understand;

- It should be a complete specification for the purposes of the development agency....

- While it is being produced, the partial specification document can be ... referenced for use in developing other parts. This will also allow it to be maintained whenever the need for changes is recognized, either during the development of the proposed system or later during its operational life.

Parnas [Parn77a] also acknowledges the role of specification as frame when he asserts that a specification is necessary

- To describe the problem to be solved.

- For communication between software engineers.

- To free the programmer from needing to know how the rest of the system works.

- To support the development of multi-version software.

- To complete the description of intermediate design decisions [encapsulated, for example, in the abstract primitives that make up high-level representations in Figure 2-1].

- To permit verification of intermediate design decisions.

A specification, then, is that abstract description of a system that provides a frame for system verification, for answering the question "Did we build the product right?" [Boeh81]

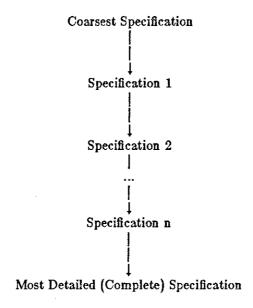

Since, as I have noted, the word "specification" is infrequently used in a VLSI design context, what part of the VLSI design model is, by virtue of addressing these purposes, a de facto specification? Consider the initial (top-level) steps in the model of VLSI design developed in section 2.1.1. Figure 2-3 expands these initial steps into their four component activities. One of these activities must be the synthesis, from the (undescribed) designer's concept, of a highest-level description of the design, a description that cannot be verified since there is no description against which it can be verified. It is this highest-level, unverified description that I call the specification of the VLSI design, and it is this description that serves as a frame for verification activities. \(^1\)

This is not to say that lower-level descriptions cannot be taken out of their context in one design hierarchy (Figure 2-1) and used as specifications in another. For example, a logic diagram might not be a specification in the context of a complete design but might serve as one in a subset of that design activity (a separate instantiation of Figure 2-1).

Figure 2-3. Expansion of the VLSI Design Process at its Highest Levels.

Many different types of specification exist. The following list describes some distinguishing characteristics important for VLSI designs.

(1) Informal vs. Formal. A specification is usually called formal if both the syntax and semantics of its primitives are mathematically precise, that is, strictly and unambiguously defined [Lisk79]. Formality and precision in specifications are, therefore, intertwined. Parnas [Parn77a] concedes that a specification can be precise without being formal but notes that creating one is "very difficult." By definition, the converse is not true: a formal specification is always precise.

Sometimes added is the stipulation that a formal specification must contain the capability to demonstrate rigorously the validity of implementation objects derived from it [Cohe83, Lehm84]. In my view, this overconstrains the definition, however desirable such a capability may be.

(2) Syntactic vs. Semantic. Wegner [Wegn84] differentiates syntactic and semantic interface specifications of software components as follows: "Syntactic interfaces specify compile-time invariants that determine how components fit together, while semantic interfaces specify execution-time invariants that determine what the component computes." A similar concept exists for IC modules: the syntax (well-formedness) of a composition of modules can be checked statically (i.e., without recourse to dynamic analysis or simulation), whereas the semantic integrity of a module

composition requires dynamic verification. Syntactic specifications, therefore, are adequate to determine the consistency (but not the validity) of a proposed module interconnection. As Wegner notes,

strong semantic interface specifications are intractable in the sense that they do not always exist and their correctness cannot always be verified. ... The trade-offs between the flexibility and efficiency of very weak interface specifications and the guaranteed integrity of strong interface specifications need to be better understood.

(3) Non-executable vs. Executable. A specification is called executable if it is possible to create a machine interpretation of the specification that provides an approximation of external system behavior [Zave84]. Because of their precise syntax and semantics, all formal specifications can be meaningfully processed by a computer [Lisk79]; however, not all formal specifications contain the kinds of behavioral semantics necessary to permit simulation of system behavior by machine processing.

An extreme (and sometimes overconstraining) form of executable specification is a realization of the desired design: when questions of specification details arise, one "asks the machine" by making an experimental query of the existing realization [Broo75].

(4) Black-Box vs. Clear-Box. Earlier, a clear-box (sometimes called structural) specification of a module interface was characterized as one that prescribed the interface indirectly by describing an implementation of internal module structure, logic, or circuitry. A black-box (or behavioral) specification, on the other hand, prescribes a module interface through a description of the module's externally visible behavior [Zave84]. Somewhat generally, I referred to a black-box interface specification as an abstract interface specification, in that for a given black-box specification more than one implementation (of the type prescribed in a clear-box specification) could exist.

This distinction is perhaps too clearly drawn. Proponents of clear-box specification might state that the implementation they produce is not meant to constrain the implementation, but merely to prescribe its behavior. Indeed, this implementation itself could be abstract, describing module behavior executably but in terms of implementation-independent substructures [Zave84]. Zave calls a specification that describes module behavior in such a way an operational specification. In contrast, a functional or input/output specification describes a direct functional relationship among module inputs and outputs without reference to substructures [Lisk79]. For this dissertation, an (abstract) operational specification is also a black-box specification, but a so-called operational specification that prescribes an implementation is neither black-box nor operational.

In this dissertation, I will thus not join the debate between proponents of operational and functional specifications. The crucial issue is that both types can specify interfaces abstractly, and I contend that such specification, which I call black-box, is superior to its clear-box counterpart. Furthermore, in the hardware domain much of what passes for operational specification, as Zave defines it, is in practice clear-box specification.

#### 2.1.4 Module Function; Module Performance.

Definitions. The function of an IC module is its externally visible behavior. The performance of an IC module is a set of measurements of its function in terms of physical phenomena (e.g. speed, power, area).

Discussion. The word "functional" is overloaded in specification parlance. In distinction from the use made of it in the previous section as an opposite to "operational," it can also be used to differentiate the semantics contained in the specification.

In software, Liskov and Berzins [Lisk79] state that "functional" specifications "describe the effect of the module on its external environment," whereas "performance" specifications "describe constraints on the speed and resource utilization of the module." In IC design, however, the effect of the module on its external environment depends on its performance, so that the line between functional and performance specifications must be redrawn. Indeed, it is possible to think of a single function/performance continuum, corresponding to a continuum of abstraction of specification primitives. I will treat this issue in detail during the discussion of adequacy in section 2.2.2.

Other-than-functional specifications are sometimes called constraints. Roman [Roma85], in a recent taxonomy of software requirements engineering issues, enumerates several constraints besides performance: interface constraints (assumptions about the environment), operating constraints (size, weight, power, etc.), life-cycle constraints (maintainability, enhanceability, portability, development time limitations, etc.), economic constraints, and political constraints. For the purposes of the current VLSI-oriented work, Roman's interface constraints are considered to be orthogonal to the functional/performance issue; operating constraints are considered together with performance constraints; and the other three types of constraints can be dealt with only informally.

Figure 2-4. Continuum of Specification Refinement.

Two separate continua of refinement (Figure 2-4), one each for function and performance, thus exist in software specification.

In hardware engineering, however, a well-known adage states: "Circuits must not only work; they must perform." In hardware design, what is functionally correct under less specific parametric or performance constraints may cease to be functionally correct under more specific constraints; thus function and performance are naturally intertwined. Because of this characteristic of hardware engineering, then, in IC design what is called a functional specification can be interpreted as an early stage, and performance specification as a later stage, of a single specification refinement continuum. At all levels of refinement the specification must be precise; the primitives with which it is described, however, may vary in specificity. The adequacy, then, of an IC design abstract interface specification depends on the specificity of its performance constraints relative to the specificity required. If one's concern is merely that the circuit function correctly at some level of performance, then a less detailed (functional) specification will be adequate. But if one's concern is that the circuit function correctly at an intended level of performance, a more refined, more detailed specification will be needed.

In VLSI design in particular, concern for correct behavior at intended performance levels is of central importance. Ultimately, then, a VLSI design interface specification must contain performance detail. This requirement implies, because of the inseparability of performance from a design's geometric and electrical characteristics, that these latter characteristics must also be included. As a result, a substantial variety of information is required in a VLSI design abstract interface specification, and the specification technique employed should both (1) provide rich enough facilities to express this information and (2) express it in terms of the performance levels required.

# Shaw [Shaw84] has recently elaborated on this requirement as follows:

A specification methodology that addresses [properties other than pure functional correctness] must have two important characteristics. First, it must be possible for the programmer to make and verify assertions about the properties rather than simply analyzing the program text to derive exact values or complete specifications. This is analogous to our approach to functional specifications — we don't attempt to formally derive the mathematical function defined by a program; rather, we specify certain properties of the computation that are important and must be preserved. Further, it is important that the specification methodology avoid adding a new conceptual framework for each new class of properties. This implies that mechanisms for dealing with new programs should be compatible with the mechanisms already used for functional correctness.

#### 2.2.2 Spareness.

Parsimony, that is, limiting the number of related expressive mechanisms in a specification technique, is clearly desirable. It might fruitfully be thought of as an aspect of a more general economy, which I shall call spareness. Spareness is the property of a specification that implies that it says only what it needs to say.

As Parnas has noted [Parn72a, Parn77a], what a specification does not contain is nearly as important as what it does contain. It is vitally important not to clutter the specification with extraneous requirements: these not only over-constrain the implementer but also slow comprehension [Meye85]. Thus a spare abstract interface specification technique must not only manifest economy of expression, but it must also identify which details are essential and which are unnecessary.

# 2.2.3 Perceived Cost-Effectiveness.

The desirability of spareness is but one illustration that the usefulness of a specification is strongly related to its intuitive appeal to designers, that is, the degree to which the specification technique is perceived as cost-effective. Clarity and simplicity, as Liskov and Berzins [Lisk79]

have pointed out, contribute significantly to a specification technique's attractiveness. Choosing familiar representations also aids acceptance [Lisk79]. Finally, the costs of using the method need to be reduced as much as feasible: a clumsy or slow user interface is certain to undercut adoption of a proposed technique, especially considering that designers have not yet embraced specification methods per se. Baroque and unusable specification methods are all too easy to develop: Liskov and Zilles [Lisk75] called difficulty in use "the fundamental problem with specifications."

# 2.2.4 Malleability.

A strong contributing factor in the perceived cost-effectiveness of a specification is its usefulness throughout the design life-cycle. What quality of a specification contributes to such usefulness?

A valuable but elusive goal in design is that of getting the specification "correct" the first time through careful axiomatic thinking. Several noted contemporary scientists, such as Dijkstra, believe that such a goal is achievable [Berg81], and they may ultimately be proven right. For the present, however, specifiers do not always seem to be able to foresee the later emergence of difficulties and even contradictions in the specification constraints they have established at the outset. If these specification constraints are rigid, backtracking that includes constraint modification would be impossible.

Perhaps, then, it is unfruitful to visualize specification constraints as being rigid. Instead, the constraints might better be viewed as variables, albeit with "stiff" coefficients of elasticity. (Other variables have more pliable coefficients.) I call the degree to which a specification's constraints can be viewed as variables its malleability, and I contend that malleability enhances the life-cycle utility of a specification. Malleability is not imprecision; it is the property of a specification that permits and facilitates precise constraint adjustment as necessary, in the interest of preserving the usefulness of the specification as a frame for verification throughout the design life-cycle.

Good examples of malleable specifications are the incremental (prototype-based) [Myer84] and transformation-based [Balz83, Part83] life-cycle paradigms, as contrasted to the conventional linear development model. Such methods depend on regular incorporation of feedback into the specification, which is then used directly to derive refined systems. The appeal of these non-conventional approaches may indeed be due largely to their increasing the usefulness of the

system specification in the design life-cycle.

# 2.2.5 Change Management Support.

Finally, as has been noted in chapter 1, a primary motivation for developing a new VLSI design interface specification method is to support change management. To do this, an ideal specification technique should assure the designer that internal changes to a design module that do not change the specification also do not have effects outside the boundaries of that module. This requirement thus overlaps the requirements of the preceding sections, especially those for adequacy and malleability.

# 2.3 Existing VLSI Design Interface Specification Methods.

No technique fully meeting the five requirements enumerated in the preceding section has yet been developed. At this point, I will review the important published work that has been done in developing methods for constructing VLSI design interface specifications. It is important to note that all the specification methods to be surveyed have a place in the design process; however, I shall evaluate them, using the criteria of section 2.2, specifically as candidates for interface specification methods to support change management.

#### 2.3.1 Methods for Informal Specification.

Informal specifications of IC interfaces are most often an ad hoc mixture of prose descriptions and block diagrams, intended to convey the function and/or structure of the design to a general audience. Procedures for informal specification rarely receive wide dissemination.

# 2.3.1.1 Examples.

— Lattin et al. [Latt81] mention a "200-page document" that served as the specification for the Intel iAPX-432 design and that, judging from the context, was probably at least partly informal. Indeed, it is reasonable to surmise that most major chip design projects begin with such a document. — Standard cell system documentation usually includes an informal description of cell interfaces. Module interfaces in the Stanford Cell Library [Newk83], for example, are described both in prose and in a formal mask description that can be simulated to provide more precise interface data. Informal specifications similarly are included in documentation of those silicon compiler systems [Gros83a] that are based on parameterized standard cells, such as the Concorde System of Seattle Silicon Technology, Inc. [SST84].

# 2.3.1.2 Strengths/Weaknesses.

Britton, Parker, and Parnas [Brit81a] identify the strength of informal specifications: they are easy to review for people not intimately familiar with the technical details of the project.

Since most specifications require approval by persons in this category, Britton, Parker, and Parnas suggest that software specification methods should accommodate an informal component that embodies those assumptions critical to the design and that is consistent with the formal portion of the specification.

Unless they are supplemented by a formal component, however, informal specifications are inadequate to provide a verification frame in the design of complex systems, for the reasons listed by Dasgupta [Dasg84]:

- The dynamic aspects of the architecture ... are usually specified incompletely. [This is particularly true in IC module interface specification, since the interface is semantically rich, with functional, electrical, and geometrical components, and an informal specification is usually truncated for manageability before all these data are included.]

- It is extremely difficult, even in principle, for the design to be validated for correctness without constructing and testing the physical system.

- The sequence of design decisions and the rationale for them are seldom documented explicitly.

... It is virtually impossible to investigate, manipulate, or alter a design, or evaluate alternative architectures for performance characteristics, without constructing and testing the physical system. [Heninger [Heni73] blames this lack of robustness not only on the intractability of informal specifications but also on their frequent failure to include fundamental assumptions, required subsets, expected changes, and rules for treatment of undesired events.]

The inherent weaknesses of informal specifications as stand-alone system specifications are discussed in greater length by Meyer [Meye85].

#### 2.3.2 Methods for Syntactic Specification.

Syntactic interface specifications exist for verifying the integrity of a composition of modules; they are of most value when such verification is complex.

# 2.3.2.1 Examples.

The best examples of syntactic IC module interface specification are "pin-typing" schemes. Ségal [Séga81] was among the first to demonstrate such a technique, but his effort was abandoned because of incompatibility with other existing tools. Noice, Mathews, and Newkirk [Noic82] reported on the benefits of using signal-labeling conventions in the two-phase nMOS clocking discipline described by Mead and Conway [Mead80]; Karplus [Karp84] extended their work and provided a formal basis for it. Some success with a related scheme using a different set of restrictions has been reported by Poulton [Poul84]. Although he has so far used only manual verification of the embedded information, his method is compatible with existing design tools and has been reported to aid design composition significantly in more than one project involving multiple clocks [Poul85]. Newkirk and Mathews [Newk83] and the designers of the VIVID system [Rose84] have provided some syntactic pin-typing facilities in their respective design tools; no results analyzing their usefulness have yet been reported.

## 2.3.2.2 Strengths/ Weaknesses.

In the previously-cited quote, Wegner [Wegn84] stated correctly that although syntactic interface specifications are easier to create, it is usually in verifying semantics that a verification frame (a specification) is most required. Consequently, purely syntactic IC interface specification techniques have not yet generated much interest, except in designs, such as Poulton's, of significant syntactic complexity.

#### 2.3.3 Methods for Non-Executable Specifications.

Because informal interface specifications have already been considered, I shall examine only formal, non-executable specifications here. There have been two distinct formal, non-executable approaches, which now appear to be joining in a confluence of thought. The first approach provides a formal high-level description of both behavior and structure as a starting point for design synthesis. The second, traditionally less concerned with the specification's role in aiding synthesis, primarily describes module behavior or function with a view toward providing a frame in a formal proof of design correctness.

Synthesis-directed specification approaches begin with formal descriptions written in documentation languages that normally capture both behavior and structure of the intended design. Many of these languages are called Computer Hardware Description Languages (CHDLs). While interpreters have been created to render some of these CHDLs executable, in the main their purpose has been documentary, and their role in the specification process has been as an informal point of reference during design elaboration.

There is a class of synthesis-directed languages in which the role of capturing a starting point for synthesis so far outweighs the specification role that the languages are rarely referred to as CHDLs. These might be called "generator source languages," because their role is analogous to that of software source languages. Descriptions written in such languages (1) usually constitute an intermediate step between a (perhaps informal) specification and lower-level synthesized descriptions, and (2) serve as input to generators that produce executable design descriptions. Here are included primarily input languages for automated synthesis aids, such as chip assemblers [Mudg81, Katz83, Katz84] and silicon compilers [Gray82, Ance83, Lipt83, SST84].

Proof-directed specification approaches have undergone a change of direction. They began with non-executable specifications, such as the non-procedural functional language used by Wagner in 1977 and cited by Barrow [Barr84]; such specifications were reconciled with synthesized designs using manual proof techniques. Lately, however, with the renewed interest in artificial intelligence, more interest has been shown in creating proof-directed specifications that can be executed by inference engines to prove design correctness automatically; thus most contemporary proof-directed specifications are executable.

A natural question, raised by Cohen at the 1983 International Conference on VLSI [Cohe83], is whether a single interface specification technique could serve both synthesis and verification needs. That is, can a single technique capture sufficiently the behavior and structure of the desired design to guide the synthesis effort, while at the same time being precise enough to support formal proof of design correctness?

# 2.3.3.1 Examples.

Since Dallen [Dall83], Dasgupta [Dasg84], and Nash [Nash84] provide excellent surveys of CHDLs, it suffices to note here that CHDLs can be grouped into three classes, the block languages (e.g. PMS [Siew82]), the register-transfer (R-T) languages (e.g., CDL [Chu74], DDL [Diet74,

Maru85], ISP [Siew82], ISPS [Barb82]), and the graphical languages (e.g., Petri nets [Pete77], Patois [Dall83], Interface-Nets [Moln85]).

CHDLs have proliferated furiously [Wern84]. One current trend is toward a consensus CHDL; an international group has been working for more than ten years on such a language, CONLAN [Pilo85]. Another current trend seems to be toward extensible omnibus CHDLs that can be used to describe in a single language function, structure, and layout (e.g., the VHSIC Hardware Description Language (VHDL) currently under development by Intermetrics for the U.S. Department of Defense [Dewe84, Shah85] and GTE Laboratories' Zeus [Lieb85]). Finally, fine results have been obtained using programming languages as CHDLs, such as the use by Blazuw of APL for this purpose [Blaa76, Blaa83].

Barrow's VERIFY system [Barr84], although not properly a member of this section because it produces executable specifications, typifies the state of the art in proof-directed specification approaches. He begins with a set of primitive modules, represented as finite-state machines with known black-box function. Next, he composes these modules into the structure of the target design. Finally, he uses a PROLOG-based interpreter to prove that the mathematical composition of the functions making up the interconnection is the function of the target design.

Can a single specification support both synthesis and verification? Frankel and Smoliar [Fran79], Rowson [Rows80], Gordon [Gord81], Cardelli and Plotkin [Card81], Hafer and Parker [Hafe83], and Sheeran [Shee84] have all suggested the feasibility of specifications that apply mathematical compositional systems to VLSI design components. Subrahmanyam [Subr83] has recently reported on the development of a theoretically precise specification language designed to serve as input to a silicon compiler, thereby showing a fortiori that it can serve to guide manual design synthesis.

#### 2.3.3.2 Strengths | Weaknesses.

Formal specification methods have substantial potential for dealing with the complexity levels inherent in VLSI design, in that they can capitalize on their foundations in discrete mathematics and the theory of computation. Nevertheless, the formalism in such methods is now largely foreign to programmers and managers, even to those with engineering backgrounds. If these methods could be interpreted in automated tools, the retraining necessitated by their introduction would be lessened, although certainly not eliminated. But methods not optimized for the use of

such tools, such as non-executable formal specifications (which now usually require a manual interface), will be slow to be accepted.

On the other hand, methods that are familiar, such as clear-box specification using CHDLs, will be abandoned reluctantly, and the use of such techniques is currently widespread [Dasg84, Evan85]. CHDLs for black-box specification, whose primitives are abstract, do not have the same intuitive appeal, however. Because no CHDL has emerged as a standard after many years [Wern84], a needed breakthrough in CHDL technology may still be lacking.

# 2.3.4 Methods for Clear-Box Specification.

Since non-executable specifications were addressed in the preceding section, only executable clear-box specifications will be covered here.

Clear-box VLSI specification methods are an evolution of specification techniques used at lesser degrees of integration. The primary characteristic of such clear-box specifications is that they prescribe interfaces by inference, rather than directly.

# 2.3.4.1 Examples.

Executable clear-box specifications can be classified according to the level of abstraction of the primitives appearing in the clear box. The executable clear-box CHDL specifications have the highest-level primitives, such as registers. Next, generally for smaller modules, are found the ubiquitous logic diagrams and their simulators. These are especially prevalent in the composition of systems consisting of SSI and MSI circuits. Finally, in cases in which a replacement for an existing module is being developed, circuit- and mask-level simulators are available to enable the existing module to act as the specification. Each technique is widely used, and there are many languages and simulators for this purpose.

Excellent results have been reported from the use of a clear-box specification system by Dussault, Liaw, and Tong at AT&T Bell Laboratories [Murp83, Duss84]. This tool, called the Functional Design System (FDS), enables designers to construct circuits hierarchically using custom-designed primitives tailored from a menu of options. Designers can work with black-box descriptions of each primitive written in a special executable language. FDS is currently being used in a production environment.

## 2.3.4.2 Strengths | Weaknesses.

Clear-box specifications, like informal specifications, have the advantage of being familiar to designers. They also provide a path to a feasible implementation, whereas black-box specifications can mask fatal implementation difficulties [Moln85]. From a VLSI design point of view, however, clear-box specifications also have several disadvantages, as section 1.3.1.1 states. The most serious is that they confuse architecture (the external view) with implementation, elevating low-level concerns too early in the design process to achieve good design partitioning and unity. Furthermore, as Parnas notes [Parn77a], it becomes "very hard for both the reader and writer of specifications to distinguish requirements from peculiarities of the sample implementation." Thus clear-box specifications may constrain the implementation unnecessarily.

Zave [Zave84] lists further difficulties. Clear-box specifications are complex; often not taking advantage of abstraction, they scale up poorly and are hence reduced in value at VLSI levels of integration. Furthermore, because of this level of detail, they are time-consuming to construct and analyze. Finally, Dallen [Dall83] contends that clear-box specifications do not naturally aid the synthesis process in hierarchical design because they are usually tied to fixed levels of abstraction.

# 2.3.5 Methods for Formal, Semantic, Executable, Black-Box Specification.

Because critical disadvantages exist with each method of VLSI design interface specification discussed thus far, examining the intersection of their complements provides the best hope for finding techniques meeting the five requirements of section 2.2.

Functional specification using high-level programming languages or special-purpose specification languages is the primary technique that appears in this intersection. Typically, a black-box interface specification is constructed for the module under design, a high-level language is used to describe its behavior, and the simulated output is compared to that obtained by simulating lower-level representations of the design. Evaluation of the specification through simulation, rather than through analysis or prototyping, is almost always used because of the intractable complexity of the specification at VLSI levels of integration. Special-purpose specification languages have arisen because programming languages can be cumbersome to use for this purpose: they do not handle timing in a natural way, and it is difficult to make specifications written in them grow with the design life-cycle.

# 2.3.5.1 Examples.

Many designers use languages such as APL, Algol, BLISS, C, and Pascal for functional simulation of system specifications [Dall83, Evan85]. Lattin et al. [Latt81] used a high-level language, SIMULA, directly as the specification medium for the Intel iAPX-432 chip. That is, rather than serving as a simulator for a separate specification, this simulator itself filled the role of the frame for design verification; questions were resolved by "asking the machine." Tham, Willoner, and Wimp [Tham84] of Intel updated this technique in their recent use of a MAINSAIL frame; a similar approach was also used by the designers of the Hewlett-Packard FOCUS chip [Cane83]. The MetaLogic, Inc., MetaSyn silicon compiler [Sisk82] accepts as input a LISP-like executable description of the function to be implemented [Wall84]. Control Data Corporation's MIDAS system specifies designs using a programming language enhanced with timing semantics [Evan85]. Finally, Suzuki has used Concurrent Prolog to specify the function of the Dorado computer [Suzu85].

Parker and Wallace [Park81] identify the following milestones in the history of specialpurpose black-box interface specification languages:

- Bell and Newell's port semantics [Bell71];

- -- Curtis's Interface Description Language [Curtis], a multi-level extension of PMS and ISP developed circa 1974-1975;

- Vissers's formal description<sup>2</sup> of state diagrams using APL enhanced with timing constructs [Viss76]; and

- Marino's proposed MPLID [Mari78], a language for specification of hierarchical module interfaces.

Parker and Wallace's own language, SLIDE (Structured Language for Interface Description and Evaluation), synthesizes these developments into an executable black-box register-transfer language. SLIDE's major contributions are this synthesis of trends and its elegant facility for describing module interconnections as communicating asynchronous concurrent processes.

<sup>&</sup>lt;sup>2</sup> See also [Blaa76].

|                                     | Pin names/attributes                                     | Parameters                   |

|-------------------------------------|----------------------------------------------------------|------------------------------|

| Т1                                  | ( K/unspecified<br>( L/input<br>( M/unspecified          | shape=6<br>lineage=pure-enh. |

| <b>T</b> 2                          | ( N/unspecified<br>( P/input<br>( Q/unspecified          | shape=3<br>lineage=pure-enh. |

| T1/T2<br>composed<br>in<br>parallel | (K/unspecified<br>(L/input<br>(P/input<br>(M/unspecified | shape=2<br>lineage=pure-enh. |

Figure 2-5. Bain's External Outlines [Bain84].

Several other interesting approaches have recently been taken to the development of executable special-purpose languages for black-box VLSI design interface specification. For example, Bain [Bain84] has incorporated into his CHECK-ME design methodology verification system a technique, based on Penfield's [Penf72] "wiring operators," which completely characterizes a circuit using an "external outline" consisting of a list of terminal names, a limited set of input/output attributes, an electrical drive factor based on the shape of the internal transistors, and a broad characterization of the implementation strategy that he calls "lineage" (Figure 2-5). While it requires extension to achieve semantic adequacy at greater levels of specification refinement, Bain's method is encouraging, for it illustrates the simplicity that can be achieved in abstract IC circuit interface specifications if an appropriate set of abstractions is identified.

Tsai and Achugbue [Tsai83] provide in their BURLAP system an idea of what a timing-level extension of Bain's external outline might look like. They specify the abstract interface by a "multi-cell module" (MCM) description consisting of the components listed in Figure 2-6. Figure 2-7 shows the contents of a typical BURLAP specification.

The hierarchy exploited by Bain and by Tsai and Achughue has been formally analyzed by Chen and Mead [Chen83]. Using mathematical methods, they define a semantic hierarchy of specification, and of the ensuing verification by simulation, similar to that depicted in Figure 2-4. In this way, they formally partition the design process and suggest that a uniform representation can be used to provide interface descriptions as simulator input at all levels. Individual design

```

I/O Interface

indicates the pin names and the pin types

at the "black box" level.

description of the block function, either

Behavioral

in a procedure or Boolean equations

(truth table).

description of the interconnection of the

Structural

low-level primitive elements into which the

MCM can be expanded [not used in black-box

specification.

description of the layout and size of the MCM.

Physical

delay and timing information used by logic

Electrical

simulator and timing verifier.

```

Figure 2-6. Components of a BURLAP Interface Specification [Tsai83].

```

Begin_Cell

Name:

RAM32x8

Class:

Storage_Element

Physical

Cell_Width:

40

Cell_Height:

40

Pin_Count:

23

Electrical

Cell_Current:

35mA

Power_Dissipation:

150mW

Delay:

60ns

Pins

Pin_Name:

A0

Pin_Type:

IN

Capacitance:

0.1pf

Equivalent_Port:

0,38

Layer:

Polysilicon

Pin_Name:

Pin_Type:

OUT

Capacitance:

0.15 pf

40,38

Equivalent_Port:

Layer:

Polysilicon

[Pin_Name:

...]

Power-Bus/Clock

VSS_Width:

3

VSS_Port:

38,0

End_Cell

```

Figure 2-7. A BURLAP Specification of a Static RAM [Tsai83].

modules, in their work, are conceived as separately-compilable MAINSAIL descriptions of finitestate machines, encapsulating design details at appropriate levels of semantic abstraction. To date, however, their work has centered on creating the formal bases necessary to prove correctness, rather than on developing an abstract interface specification technique tractable at VLSI levels of integration.

Another special-purpose specification language, previously cited, that makes use of separately-compilable modules that represent finite-state machines is included in Barrow's VER-IFY system [Barr84]. VERIFY also uses the hierarchical approach recommended by Chen and Mead to predict the functional behavior of an interconnection of these modules from a description of the behavior of each. But, instead of using the simulation customary in the verification process, VERIFY uses a PROLOG-based interpreter to compare the predicted behavior with a set of equations that specify the system's behavior. To date, VERIFY has been tested on functional specifications only, but its approach to verification is encouraging, in that it can be replicated hierarchically to scale up to VLSI design levels without the need for specifications to be reexecuted at each level of refinement. A sample VERIFY specification is shown in Figure 2-8.

The inherent complexity of VLSI-level system specifications has hindered not only verification but also the development of silicon compilers, the hardware design counterpart of the transformational implementation of operational specifications mentioned by Zave [Zave84]. Subrahmanyam [Subr83] has addressed both problems simultaneously in his specification formalism called BehaviorExpressions, an algebraic specification language designed also to serve as input to a high-level silicon compiler. Figure 2-9 gives an example of a specification expressed in this language.

Subrahmanyam's work addresses the need for semantic adequacy at each of the functional, geometric, and electrical levels mentioned earlier; it also includes paradigms for instructing the silicon compiler to consider performance and cost data in performing its transformations. His research plan is comprehensive and ambitious, and its results could prove significant indeed.

# 2.3.5.2 Strengths/Weaknesses.

Functional interface specification with abstract high-level languages has achieved the most promising results of any technique discussed. Specification refinement, however, requires the eventual representation of dense semantics (particularly geometric and electrical information, concurrency, and parallelism). Although it is possible to express such semantics and their complex data types in conventional programming languages, not many designers are now familiar with the

```

% Definition of module type Register

Module: reg

Ports:

in (input, integer)

out (output, integer)

State Variables:

contents (integer)

Output Equations:

out := contents

State Equations:

contents := in

```

Figure 2-8. A Module Specification in VERIFY [Barr84].

```

StackChip(s) =

INITIALIZE. StackChip (NEWSTACK)

+

INSERT x. StackChip (PUSH(s,x))

+

DELETE TOP(s). StackChip (POP(s));

```

where Stack is an abstract data type with predefined syntax and semantics; INITIALIZE, INSERT, and DELETE are global ports (two input and one output, respectively); s is a parameter that represents an instance of the type Stack; and NEWSTACK, PUSH, and POP are operations defined for the type Stack.

Figure 2-9. Specification Using BehaviorExpressions [Subr83].

disciplined programming style that such expression requires. Consequently, these languages are now more frequently used for functional specification alone.

Special-purpose languages possess more powerful primitives for expressing design semantics, but their degrees of perceived cost-effectiveness and malleability vary, particularly in the representation of very-large-scale designs. And, as Evanczuk notes, a special-purpose language has a smaller user community; he believes that the user momentum, availability, and portability of general-purpose programming languages makes techniques based on them more likely to succeed [Evan85].

### 2.4 Parnas's Techniques for Abstract Interface Specification.

Parnas's approach to attacking the complexity issues of the "software crisis" has been one of "divide and conquer." Few others have elucidated as well as he the issues involved in dividing the software design task. A brief review of his treatment of these issues is in order.

### 2.4.1 State Machines.

In an early paper [Parn72a], Parnas set out the *module* as his software building block and described how it was to be specified. His was a black-box specification, and his model of the black-box contents a state machine. His choice of this formal but familiar model is typical of his philosophy: understanding is the goal, and understanding is aided by simplification, without compromising precision, wherever possible.

Interaction with Parnas's module takes place entirely through what he later called access functions (or access programs). These functions make up a major part of a module's specification and can be invoked by other modules either: (1) (effect access function) to change the state of the module by providing an input value; or (2) (value access function) to read out the state of the module. By restricting access functions to one of these two types, the opportunity for prescription of an intended implementation (which would cause the specification to become clear-box) is reduced [Bart77].

### 2.4.2 Traces.

Parnas believed strongly [Parn72a] that specifications should be minimized, in the sense that only the information required for the specification should be provided "and nothing more." He felt that a chief source of specification failure was overprescription or redundancy, a view that was then controversial but that has now been generally accepted [Meye85]. With Bartussek [Bart77], Parnas became concerned that functions in the specification could potentially prescribe an implementation. To be sure, the definitions of such functions were, by fiat, unavailable outside the module being specified (leading to their being called "hidden functions" in the literature). But their existence bothered Bartussek and Parnas, especially because of the suggestion (see section 2.1.3) that modules could be specified "by giving a program whose behavior would be acceptable and asking that the program produced be 'equivalent'." Such "equivalent functions," they felt, provided superfluous information [Parn75a].

```

Syntax:

PUSH:

<integer> X

\langle stack \rangle \rightarrow \langle stack \rangle

\langle stack \rangle \rightarrow \langle stack \rangle

POP:

TOP:

<stack> → <integer>

<stack> → <integer>

DEPTH:

Semantics:

A. Legality:

(1) &(T) => &(T.PUSH(a))

(2) &(T.TOP) = &(T.POP)

B. Equivalence:

(3) T.DEPTH \equiv T

(4) T.PUSH(a).POP \equiv T

(5) &(T.TOP) => T.TOP \equiv T

C. Values:

(6) &(T) \Longrightarrow V(T.PUSH(a).TOP) = a

(7) &(T) \Rightarrow V(T.PUSH(a).DEPTH) = 1 + V(T.DEPTH)

(8) V(DEPTH) = 0

```

Figure 2-10. Specification Using Traces of a Stack for Integer Values [Bart77].

#### Notation:

Dot (.) is the functional composition operator.

&(T) is TRUE if calling the functions in the sequence specified in the trace with the arguments given in the trace when the module is in its initial state will not result in an abnormal exit.

V(T) is a value access function that returns information about the module state.

The result of Bartussek's and Parnas's work was an "axiomatic" specification approach called "traces." It is called axiomatic [Lisk79] because a specification using traces makes statements (axioms) only about the effects of function calls; it contains no reference to any internal data structure. Figure 2-10 gives an example of such a specification. Specifications using the trace approach are termed complete (i.e., they completely determine externally visible module behavior) if one can determine from the specification the value returned by every trace (sequence of function calls) ending with a value access function and not causing an abnormal exit. The use of traces for IC specification has been reported by Rem, van de Snepscheut, and Udding [Rem83].

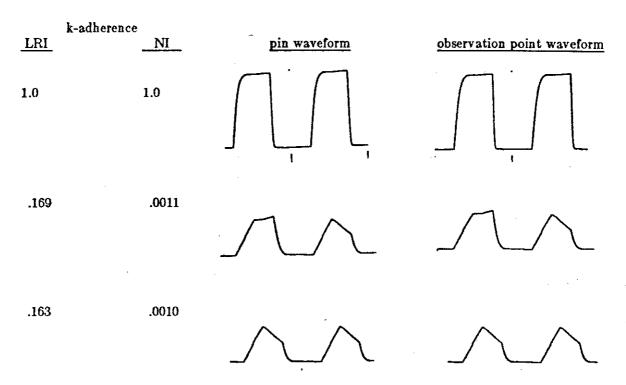

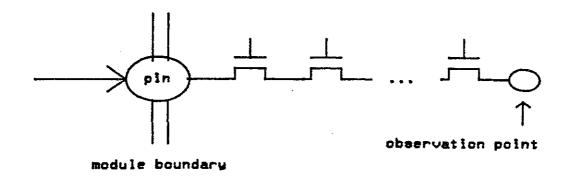

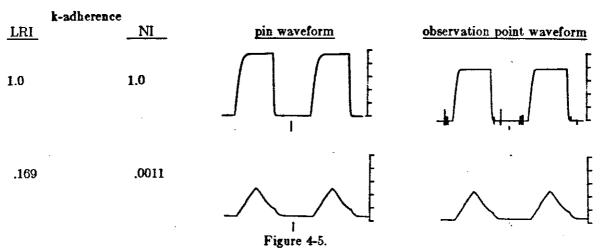

# 2.4.3 The Software Cost Reduction (SCR) Project.